2023. 11. 15. 01:17ㆍ컴퓨터공학 전공공부/논리회로

6-1. 이진수의 덧셈 & 뺄셈

이진수의 덧셈과 뺄셈

이진수의 덧셈은 십진수의 덧셈과 유사하다. 십진수에서 합이 9가 넘어가면 carry가 발생하는 것처럼, 이진수에서도 합이 1이 넘어가면 carry가 발생한다. 뺄셈 또한 십진수처럼 작동한다. 0에서 1을 빼려고 할 경우, 1을 앞에서 빌려온다.

이진수의 부호 표현

이진수에서는 magnitude(절대적인 값의 크기)만을 표현할 수 있기 때문에, 부호를 표현하고 싶으면 extra sign bit을 추가한다. 잘 사용하진 않는다.

6-2. 부호가 있는 수의 표현

2's complement

부호가 있는 수를 표현하는 대표적인 방식이다.

6-3. 2's complement 시스템에서의 덧셈

1. 일단, magnitude에 대한 이진수의 덧셈을 수행한다. 이 때 sign bit은 magnitude bits에 포함되어 있다.

2. 덧셈의 결과가 sign bit의 carry로 끝난다면, carry bit은 무시된다. 덧셈의 결과가 양수라면 pure binary 형태인 것이고, 음수라면 2's complement 형태인 것이다.

6-4. 2's complement 시스템에서의 뺄셈

덧셈과 비슷하게 수행된다.

overflow

양수 + 양수나 음수 + 음수에서 발생한다. 덧셈의 결과가 magnitude bits의 크기를 넘어가면 overflow가 발생한다. 맞지 않는 결과값이 도출된다.

number circle을 이용한 덧셈과 뺄셈

정 가운데에서 시작해 덧셈의 경우 시계 방향으로, 뺄셈의 경우 반시계 방향으로 이동한다.

6-5, 6-6. 이진수의 곱셈 & 나눗셈

이진수의 곱셈, 나눗셈 모두 십진수와 유사하다. 이진수의 나눗셈에서 나뉨수와 나눗수의 부호가 같을 경우 양수, 다를 경우 음수의 결과값이 나온다.

6-7. BCD 덧셈

십진수의 합이 9보다 작을 때 연산은 일반 이진수 덧셈과 동일하다. 십진수의 합이 10 이상이면 이진수 6 (0110)을 더한다. 예를 들어, 5 (0101)와 6 (0110)을 더하면 11(1011)이 되는데 이는 BCD 범위를 벗어난다. 이 경우, 이진수 6을 더하여 1 0001로 만든다. 1*10 + 1(0001) = 11이므로 두 수의 합을 올바르게 나타낸다.

6-8. 16진수 연산

16진수 덧셈

십진수로 변환하여 더한 다음 15 이하면 16진수로 변환하고, 16 이상이면 16을 뺀 후 다음 위치에 carry 1을 더한다.

16진수 뺄셈

이진수와 같은 방식을 사용한다.

16진수의 부호

MSD (가장 큰 자릿수)가 8 이상이면 해당 숫자는 음수이고, 7 이하면 해당 숫자는 양수이다.

6-9. 연산 회로

1. ALU (arithmetic/logic unit)

ALU는 메모리에 저장된 데이터를 수용하고, control unit의 지시에 따라 산술 및 논리 연산을 실행한다.

2. Control unit

control unit은 memory unit에 있는 특정 숫자를 accumulator register에 저장된 숫자에 더하도록 작동한다.

3. Memory unit to B register

덧셈의 결과가 memory unit에서 B register로 전해진다.

4. Accumulator register + B register

accumulator register에 있는 값과 B register에 있는 값이 logic circuits에서 더해진다. 더해진 값은 accumulator register에 저장된다. 이 값은 계속 accumulator register에 남아있거나 memory로 옮겨진다.

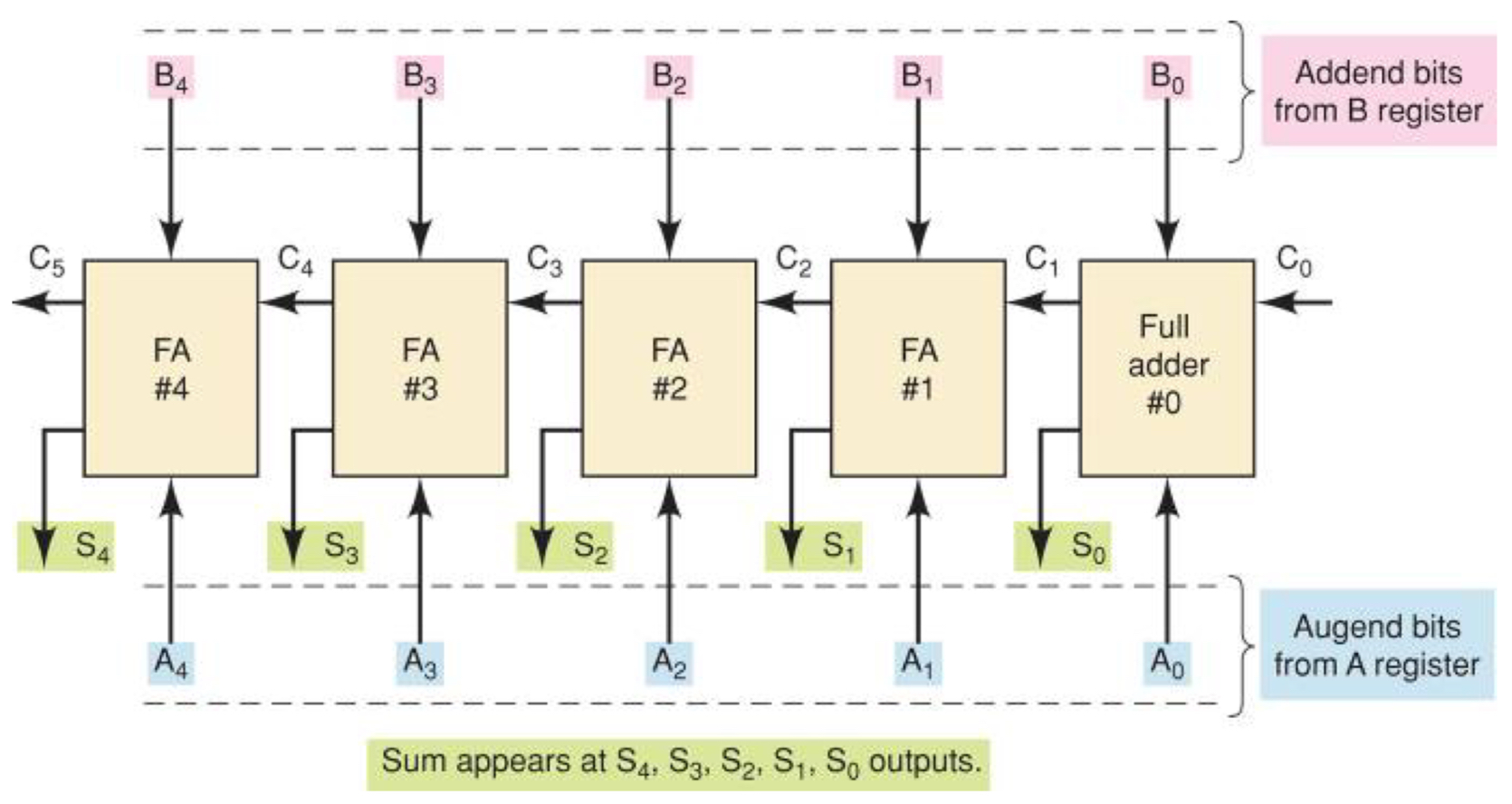

6-10. 병렬 이진 덧셈기

6-11. Full Adder의 설계

진리표

논리 회로도

6-12. 레지스터를 포함한 완전한 병렬 덧셈기

회로를 이용한 1001 (2진수)와 0101 (2진수)의 덧셈

1. t1에서 CLR 펄스가 적용된다.

2. t2에서 1001이 memory에서 B register로 전송된다.

3. t3에서 1001과 0000의 합이 A register로 전송된다.

4. t4에서 0101이 memory에서 B register로 전송된다.

5. t5에서 덧셈의 결과가 A register로 전송된다. > 두 이진수의 덧셈이 accumulator에 저장돼 있다.

대괄호

[]는 register의 내용을 나타낸다. 예를 들어 [A] = 1011은 A3=1, A2=0, A1=1, A0=1을 나타낸다. (A는 register)

데이터 전송

레지스터의 데이터 전송은 화살표로 표현된다. 예를 들어 [B] → [A]는 register B의 내용이 register A로 전송됐음을 뜻한다.

6-13. Carry 전파

carry로 인한 속도 지연

병렬 덧셈기의 속도는 carry 전파때문에 제한되어 있다. (carry ripple이라고도 불린다.) 다시 말해, carry bits가 ripple될 때까지 기다려야 하는 것이다. 비트가 추가되면 더 많은 지연이 발생한다.

고속 장치에서는 지연을 줄이기 위해 '미리보기 캐리 방식 (look-ahead carry scheme)'이 일반적으로 사용된다.

6-14. 집적회로 병렬 덧셈기

가장 흔한 병렬 덧셈기는 4비트 장치이다. 한편 4비트 장치 두 개를 연결한 8비트 장치를 사용하기도 한다.

6-15. 2's complement 시스템에서의 병렬 덧셈기

덧셈기를 이용해 음수와 양수를 더할 때

음수를 2's complement 형태로 바꾼 다음 정상 덧셈을 수행한다.

이를 이용하여 뺄셈을 수행하는 덧셈기도 만들 수 있다. (A+B = A+(-B)임을 이용한다.)

덧셈과 뺄셈을 모두 수행하는 병렬 덧셈기

6-16. ALU (Arithmetic & Logic Unit) 집적회로

6-17. 병렬 덧셈기의 문제 해결

mode 1. ADD = 0, SUB = 0

덧셈의 결과가 A 레지스터에 있는 값에 1을 더한 것과 항상 같다.

mode 2. ADD = 1, SUB = 0

덧셈의 결과가 정상 결과값보다 항상 1 크다.

mode 3. ADD = 0, SUB = 1

덧셈의 결과가 항상 [A] - [B]와 같다.

'컴퓨터공학 전공공부 > 논리회로' 카테고리의 다른 글

| 논리회로 chap 9. MSI Logic Circuits (1) | 2023.12.04 |

|---|---|

| 논리회로 chap 5. Flip-Flops and Related Devices (0) | 2023.12.04 |

| 논리회로 chap 7. Counters and Registers (2) | 2023.11.28 |